UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| APPLICATION NO.           | FILING DATE   | FIRST NAMED INVENTOR                | ATTORNEY DOCKET NO. | CONFIRMATION NO. |

|---------------------------|---------------|-------------------------------------|---------------------|------------------|

| 11/372,198                | 03/10/2006    | Atsushi Kuwata                      | MA-674-US           | 4344             |

|                           | 7590          | <sup>2</sup><br>RTY LAW GROUP, PLLC | EXAM                | INER             |

| 8321 OLD COU              | JRTHOUSE ROAD |                                     | DUDEK JR,           | EDWARD J         |

| SUITE 200<br>VIENNA, VA 2 | 22182-3817    |                                     | ART UNIT            | PAPER NUMBER     |

|                           |               |                                     | 2186                |                  |

|                           |               |                                     |                     |                  |

|                           |               |                                     | MAIL DATE           | DELIVERY MODE    |

|                           |               |                                     | 01/12/2012          | PAPER            |

Please find below and/or attached an Office communication concerning this application or proceeding.

The time period for reply, if any, is set in the attached communication.

## UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE BOARD OF PATENT APPEALS AND INTERFERENCES

Ex parte ATSUSHI KUWATA

Appeal 2010-003807 Application 11/372,198 Technology Center 2100

Before HOWARD B. BLANKENSHIP, THU A. DANG, and DEBRA K. STEPHENS, *Administrative Patent Judges*.

DANG, Administrative Patent Judge.

### **DECISION ON APPEAL**

## I. STATEMENT OF THE CASE

Appellant appeals under 35 U.S.C. § 134(a) from a Final Rejection of claims 1, 3-17, and 19-31. Claims 2 and 18 have been canceled. We have jurisdiction under 35 U.S.C. § 6(b).

We affirm.

## A. INVENTION

According to Appellant, the invention relates to a disk array device using a high-speed throughput bus and a shared memory device thereof, a control program and a control method of the disk array device (Spec. 1, Il. 6-12).

### B. ILLUSTRATIVE CLAIM

Claim 1 is exemplary:

1. A disk array device, comprising:

a director device which manages input/output of data to/from an external device and a disk drive device; and

a shared memory device having a cache memory for input/output data,

wherein said director device transmits a command for instructing on control of the cache memory for said input/output data to said shared memory device, and said shared memory device executes control of said cache memory for said input/output data based on a command from said director device,

wherein said director device includes:

a command control unit which transmits said command and receives a processing result for said command which is sent from said shared memory device,

wherein said shared memory device includes:

a processing unit which executes control of said cache memory for said input/output data based on a command from said director device, and

a command control unit which receives a command from said director device and transmits a processing result for said command from said shared memory device, and

wherein the command control unit of said director device is connected to the command control unit of said shared memory device by a serial communication bus.

#### C. REJECTION

The prior art relied upon by the Examiner in rejecting the claims on appeal is:

| Millard     | US 4,096,567    | Jun. 20, 1978 |

|-------------|-----------------|---------------|

| Scaringella | US 6,467,047 B1 | Oct. 15, 2002 |

| Fujimoto    | US 6,477,619 B1 | Nov. 05, 2002 |

Claims 1, 3-13, 16, 17, 19-22, and 25-31 stand rejected under 35 U.S.C. § 103(a) as being unpatentable over Fujimoto and Millard.

Claims 14, 15, 23, and 24 stand rejected under 35 U.S.C. § 103(a) as being unpatentable over Fujimoto, Millard and Scaringella.

#### II. ISSUE

The dispositive issue before us is whether the Examiner has erred in concluding that Fujimoto in view of Millard would have suggested a "director device" that includes "a command control unit which transmits said command and receives a processing result for said command which is sent from said shared memory device" and a "shared memory device" which includes "a command control unit which receives a command from said

director device and transmits a processing result for said command" wherein "the command control unit of said director device is connected to the command control unit of said shared memory device by a serial communication bus" (claim 1). In particular, the issue turns on whether Fujimoto in view of Millard would have suggested a serial communication bus connecting a command control unit of a director device and a command control unit of a shared memory device.

### III. FINDINGS OF FACT

The following Findings of Fact (FF) are shown by a preponderance of the evidence.

## *Fujimoto*

1. Fujimoto discloses a disk array controller 1 that includes channel interface (IF) units 11 for interfacing with host computers 50, disk IF units 12 for interfacing with hard disk drives 5, shared memory units 13, and cache memory units 14; wherein, the channel IF units 11, disk IF units 12, and the shared memory units 13 are connected by an interconnection 210 and the cache memory units 14 are connected by another interconnection 220 (col. 6, 11, 42-56; Figs. 7 and 8).

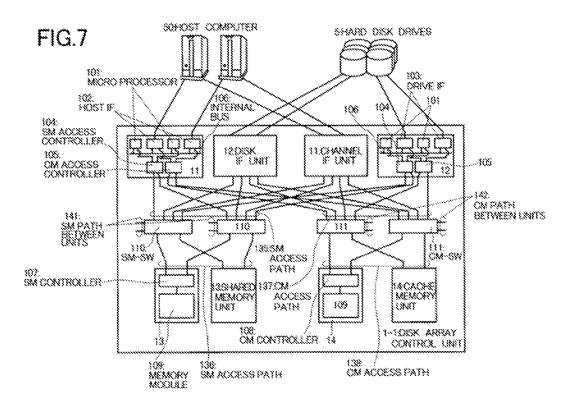

## 2. Fujimoto's Fig. 7 is reproduced below:

Fujimoto's Fig. 7 discloses a channel IF unit 11 that includes two microprocessors 101 for controlling the data transaction with the host computers 50, an SM access controller 104 for controlling the access to the shared memory units 13, and a CM access controller 105 for controlling the access to the cache memory units 14 (col. 7, 11. 6-15).

- 3. As shown in Fig. 7, the cache memory unit 14 includes a cache memory (CM) controller 108 and a memory module 109, and temporarily stores data to be recorded (col. 7, 11. 43-46).

- 4. The microprocessors 101 and host IFs 102 are connected by an internal bus 106, and the CM access controller 105 is connected directly to the two hosts IFs 102 (col. 7, ll. 15-18), while the CM access controller 105

is connected to the two CM-SWs 111 by two CM access paths 137, and the CM-SWs 111 are connected to the two CM controllers 108 by two access paths 138, enabling each CM controller 105 to have two access routes to each CM controller 108 (col. 7, 11. 58-64).

## Millard

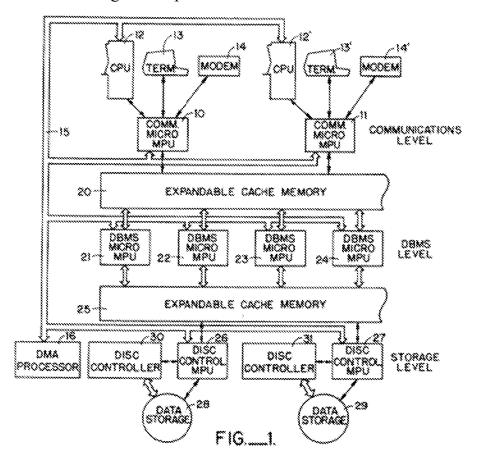

## 5. Millard's Fig. 1 is reproduced below:

Millard's Fig. 1 discloses an information storage facility with multiple level processors wherein a direct memory access bus is provided which enables high speed data transfer among the several processors included within the storage facility and also external host computers or intelligent terminals (Abstract).

6. The communications level processor is configured to communicate with a host computer, an intelligent terminal or other processor devices on a serial, parallel or DMA basis and performs all communication functions with such external devices (col. 2, 1l. 57-63).

### IV. ANALYSIS

Claims 1, 3-13, 16, 17, 19-22, and 25-31

Appellant contends that "there is no demonstration [in the cited references] of: '... wherein the command control unit of said director device is connected to the command control unit of said shared memory device by a serial communication bus', as required by independent claim 1" (App. Br. 11). In particular, Appellant contends that "neither Fujimoto nor Millard has the structural components described in even the independent claims, including the two command control units, let alone a high speed serial bus interconnecting these two components" (App. Br. 12). Appellant then contends that "Fujimoto does not have its two interfaces (e.g., the channel IF unit 11 and the disk IF unit 12) controlled by a single entity such as the director device of the claimed invention" and thus Fujimoto and Millard's "architectures are distinctly different from each other and from the claimed invention" (App. Br. 13).

However, the Examiner finds that "Fujimoto consists of disk array controllers that are all interconnected to each other and function to control access to disk drives from host computers" (Ans. 18). In particular, the Examiner finds that "Fujimoto describes the connections between all the components of the system" and notes that though "[t]he specific type of bus is not disclosed by Fujimoto . . . , there are two types of busses that

exist[s](sic) for this purpose, parallel or serial" (Ans. 17). The Examiner then concludes that "when the combination of Fujimoto and Millard is made there would be additional processors for the shared memory devices" and notes that such combination "would result in an interconnection of multiple processors, which Millard disclosed can be done with a serial bus" (Ans. 18).

Though in the Reply Brief, Appellant admits that "'Host IF' 102 [of Fujimoto] corresponds to the 'director device' of the claim," that "microprocessor 101 [of Fujimoto] would have to correspond to the 'command control unit' of the claim," and that "shared memory device having a cache memory' . . . . would have to be the 'Cache Memory Unit' 14 described as having a cache memory 109 and controller 108" (Reply Br. 2), Appellant argues that "[t]here clearly is no serial bus interconnecting microprocessor 101 with CM controller 108" in Fujimoto (Reply Br. 3). Appellant contends that "the conventional wisdom for interconnecting two processors used for disk array devices is by way of using a shared bus" (Reply Br. 3). Thus, Appellant contends that "even if Millard were properly combinable with Fujimoto, there would still be no suggestion of providing a dedicated . . . high speed serial bus specifically for [the] purpose of transmitting commands and returned processing results" (Reply Br. 4 (emphasis omitted)).

Appellant's arguments that "Fujimoto does not have its two interfaces ... controlled by a single entity" (App. Br. 13) and that there are "no suggestion of providing a dedicated ... high speed serial bus specifically for [the] purpose of transmitting commands and returned processing results" (Reply Br. 4 (emphasis omitted)) are not commensurate in scope with the

recited language of claim 1. That is, claim 1 does not require a "single" entity controlling two interfaces or any bus "specifically for purpose of transmitting commands and returned processing results" as Appellant contends. Rather, claim 1 merely requires that the command control unit of the director device is connected to the command control unit of the shared memory device by a "serial communication bus." Further, since claim 1 does not define as to what a "director device" is to mean, include or represent, contrary to Appellant's argument (App. Br. 13), claim 1 does not preclude a "director device" that comprises a plurality of separate interfaces that perform separate functions. Accordingly, in this Appeal, we address whether the teachings of Fujimoto in view of Millard would have suggested a serial communication bus connecting a command control unit of a director device and a command control unit of a shared memory device, as specially required by claim 1.

Fujimoto discloses a disk array device comprising interfaces that manage input/output of data to/from an external device and a disk drive device (FF 1) and shared memory units including a cache memory for input/output data (FF 3), wherein the interfaces comprise microprocessors for controlling the data transaction with the shared memory units and the cache memory comprises a cache memory controller and a memory module (FF 2-3). We find Fujimoto's interfaces to comprise "a director device which manages input/output data to/from an external device and a disk drive device" and find Fujimoto's microprocessor of the interfaces as "a command control unit which transmits said command and receives a processing result" as recited in claim 1. We also find Fujimoto's shared memory units to comprise "a shared memory device having a cache memory for input/output

data" wherein the cache memory controller comprises "a processing unit which executes control of said cache memory" and "a command control unit which receives a command from said director device" as recited in claim 1. In fact, even Appellant admits that "Host IF' 102 [of Fujimoto] corresponds to the 'director device' of the claim," that "microprocessor 101 [of Fujimoto] would have to correspond to the 'command control unit' of the claim," and that "shared memory device having a cache memory' . . . . would have to be the 'Cache Memory Unit' 14 described as having a cache memory 109 and controller 108" (Reply Br. 2).

Furthermore, Fujimoto discloses that microprocessor 101 and host IF 102 are connected, whereby CM access controller 105 is connected to host IF 102 (FF 4). We find microprocessor 101 to be connected to CM access controller 105. Furthermore, CM access controller 105 is also connected to CM controller 108 (*id*). Accordingly, we find microprocessor 101 to be connected to CM controller 108 via CM access controller 105. Thus, we find Fujimoto discloses that the command control unit of a director device is connected to the command control unit of the shared memory device as required by claim 1.

We thus agree with the Examiner's finding that "Fujimoto describes the connections between all the components of the system" (Ans. 17). Further, we find no error with the Examiner's finding that, though "[t]he specific type of bus is not disclosed by Fujimoto . . . , there are two types of busses that exists for this purpose, parallel or serial" (Ans. 17). In fact, as Millard discloses, communications between processors, a host computer, an intelligent terminal or other processor devices may be on a serial or parallel basis (FF 6). That is, Millard discloses the use of direct communication bus

(serial or parallel) to enable high speed data transfer among the several processors included within the storage facility and also external host computers or intelligent terminals (FF 5-6).

Accordingly, we find no error in the Examiner's conclusion that Fujimoto in view of Millard would have suggested a serial communication bus connecting a command control unit of a director device and a command control unit of a shared memory device as required by claim 1. That is, contrary to Appellant's contention (App. Br. 12), we conclude that Fujimoto in view of Millard do at least suggest two command control units, wherein "a high speed serial bus interconnecting these two components" (App Br. 12) is provided therebetween.

Although Appellant also argues that, because "architectures are distinctly different from each other and from the claimed invention," the prior art teachings "preclude a conclusion of obviousness" (App. Br. 13), Appellant appears to have viewed the references from a different perspective than the Examiner. The issue here is not whether the ordinarily skilled artisan would have added Millard's system with Fujimoto's system but whether the artisan, upon reading Millard, would find it obvious to use a serial bus for high speed data transfer as the communication bus of Fujimoto. The Supreme Court has determined that the conclusion of obviousness can be based on the interrelated teachings of multiple patents, the effects of demands known to the design community or present in the marketplace, and the background knowledge possessed by a person having ordinary skill in the art. *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 416 (2007).

Here, both Fujimoto and Millard are directed to the same field of endeavor of cache memory control. We conclude that such application of Millard's serial bus for high speed data transfer as the bus for data transfer in Fujimoto is no more than a simple arrangement of old elements with each performing the same function it had been known to perform, yielding no more than one would expect from such an arrangement. *KSR*, 550 U.S. at 416. The skilled artisan would "be able to fit the teachings of multiple patents together like pieces of a puzzle" since the skilled artisan is "a person of ordinary creativity, not an automaton." *Id.* at 420-21. As stated by the Supreme Court, an obviousness "analysis need not seek out precise teachings directed to the specific subject matter of the challenged claim, for a court can take account of the inferences and creative steps that a person of ordinary skill in the art would employ." *Id.* at 418. *See also Dystar Textilfarben GmbH & Co. Deutschland KG v. C.H. Patrick Co.*, 464 F.3d 1356, 1368 (Fed. Cir. 2006).

Accordingly, we find that the Examiner did not err in rejecting independent claim 1 over Fujimoto in view of Millard.

As for independent claims 17, 26, and 29, Appellant merely repeats the claim language (App. Br. 16) but does not provide arguments separate from those of claim 1 (App. Br. 17-18). As discussed above with respect to claim 1 which recites similar features, we conclude that Fujimoto in view of Millard would have suggested the recited features. As a result, we find that the Examiner also did not err in rejecting independent claims 17, 26 and 29 over Fujimoto in view of Millard. Appellant does not provide arguments for claims 3-13, 16, 19-22, and 25, 27, 28, 30 and 31 separate from those of claims 1, 17, 26, and 29 from which they respectively depend, other than to

Application 11/372,198

say "there are no corresponding configurations in the cited references, as required by claims 7-13" (App. Br. 18). Accordingly, claims 3-13, 16, 19-22, and 25, 27, 28, 30 and 31 fall with claims 1, 17, 26, and 29.

Claims 14, 15, 23, and 24

As for claims 14, 15, 23, and 24, Appellant merely contend that "these claims are allowable for at least the same reasons that their underlying base claims are allowable as set forth above" (App. Br. 18). As discussed above with respect to claims 1 and 17 from which claims 14, 15, 23 and 24 respectively depend, we find no error in the Examiner's rejection of the claims over Fujimoto in view of Millard. Accordingly, we find that the Examiner also did not err in rejecting independent claims 14, 15, 23 and 24 over Fujimoto and Millard in further view of Scaringella.

## V. CONCLUSION AND DECISION

The Examiner's rejection of claims 1, 3-17, and 19-31 under 35 U.S.C. § 103(a) is affirmed.

No time period for taking any subsequent action in connection with this appeal may be extended under 37 C.F.R. § 1.136(a)(1)(iv).

## **AFFIRMED**

peb

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| APPLICATION NO.           | FILING DATE                        | FIRST NAMED INVENTOR     | ATTORNEY DOCKET NO. | CONFIRMATION NO. |

|---------------------------|------------------------------------|--------------------------|---------------------|------------------|

| 11/372,198                | 03/10/2006                         | Atsushi Kuwata           | MA-674-US           | 4344             |

|                           | 7590 02/23/201<br>ELLECTUAL PROPEI | 0<br>RTY LAW GROUP, PLLC | EXAM                | IINER            |

| 8321 OLD COU              | JRTHOUSE ROAD                      | DUDEK JR, EDWARD J       |                     |                  |

| SUITE 200<br>VIENNA, VA 2 | 22182-3817                         |                          | ART UNIT            | PAPER NUMBER     |

|                           |                                    |                          | 2186                |                  |

|                           |                                    |                          |                     |                  |

|                           |                                    |                          | MAIL DATE           | DELIVERY MODE    |

|                           |                                    |                          | 02/23/2010          | PAPER            |

## Please find below and/or attached an Office communication concerning this application or proceeding.

The time period for reply, if any, is set in the attached communication.

### United States Patent and Trademark Office

Under Secretary of Commerce for Intellectual Property and Director of the United States Patent and Trademark Office P.O. Box 1450

Alexandria, Virginia 22313-1450

www.uspto.gov

MCGINN INTELLECTUAL PROPERTY LAW GROUP,

PLLC

8321 OLD COURTHOUSE ROAD

SUITE 200

VIENNA, VA 22182-3817

Appeal No: 2010-003807

Application: 11/372,198

Atsushi Kuwata

## Board of Patent Appeals and Interferences Docketing Notice

Application 11/372,198 was received from the Technology Center at the Board on January 19, 2010 and has been assigned Appeal No: 2010-003807.

A review of the file indicates that the following documents have been filed by appellant:

Appeal Brief filed on: July 13, 2009

Reply Brief filed on: November 30, 2009

Request for Hearing filed on: NONE

In all future communications regarding this appeal, please include both the application number and the appeal number.

The mailing address for the Board is:

BOARD OF PATENT APPEALS AND INTERFERENCES UNITED STATES PATENT AND TRADEMARK OFFICE P.O. BOX 1450 ALEXANDRIA, VIRGINIA 22313-1450

The facsimile number of the Board is 571-273-0052. Because of the heightened security in the Washington D.C. area, facsimile communications are recommended. Telephone inquiries can be made by calling 571-272-9797 and should be directed to a Program and Resource Administrator.

By order of the Board of Patent Appeals and Interferences.

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| APPLICATION NO.           | FILING DATE                        | FIRST NAMED INVENTOR     | ATTORNEY DOCKET NO. | CONFIRMATION NO. |

|---------------------------|------------------------------------|--------------------------|---------------------|------------------|

| 11/372,198                | 03/10/2006                         | Atsushi Kuwata           | MA-674-US           | 4344             |

|                           | 7590 01/13/201<br>ELLECTUAL PROPEI | 0<br>RTY LAW GROUP, PLLC | EXAM                | IINER            |

| 8321 OLD COU              | JRTHOUSE ROAD                      | DUDEK JR, EDWARD J       |                     |                  |

| SUITE 200<br>VIENNA, VA 2 | 22182-3817                         |                          | ART UNIT            | PAPER NUMBER     |

|                           |                                    |                          | 2186                |                  |

|                           |                                    |                          |                     |                  |

|                           |                                    |                          | MAIL DATE           | DELIVERY MODE    |

|                           |                                    |                          | 01/13/2010          | PAPER            |

## Please find below and/or attached an Office communication concerning this application or proceeding.

The time period for reply, if any, is set in the attached communication.

## **UNITED STATES DEPARTMENT OF COMMERCE U.S. Patent and Trademark Office**

Address: COMMISSIONER FOR PATENTS

P.O. Box 1450

Alexandria, Virginia 22313-1450

| APPLICATION NO./<br>CONTROL NO. | FILING DATE | FIRST NAMED INVENTOR / PATENT IN REEXAMINATION | ATTORNEY DOCKET NO. |

|---------------------------------|-------------|------------------------------------------------|---------------------|

| 11372198                        | 3/10/2006   | KUWATA, ATSUSHI                                | MA-674-US           |

MCGINN INTELLECTUAL PROPERTY LAW GROUP, PLLC 8321 OLD COURTHOUSE ROAD SUITE 200 VIENNA, VA 22182-3817 EXAMINER

Edward J. Dudek

ART UNIT PAPER

2186 20100104

DATE MAILED:

Please find below and/or attached an Office communication concerning this application or proceeding.

**Commissioner for Patents**

The reply brief filed 30 November 2009 has been entered and considered. The application has been forwarded to the Board of Patent Appeals and Interferences for decision on the appeal.

/Matt Kim/ Supervisory Patent Examiner, Art Unit 2186 /Edward J Dudek/ Examiner, Art Unit 2186

## IN THE UNITED STATES PATENT AND TRADEMARK OFFICE BOARD OF PATENT APPEALS AND INTERFERENCES

In re Application of

Atsushi KUWATA

Serial No.:

11/372,198

Group Art Unit:

2186

Filed:

March 10, 2006

Examiner:

Dudek

For: DISK ARRAY DEVICE AND SHARED MEMORY DEVICE THEREOF, AND CONTROL PROGRAM AND CONTROL METHOD OF DISK ARRAY DEVICE

Commissioner of Patents Alexandria, VA 22313-1450

#### APPELLANT'S REPLY BRIEF ON APPEAL

Sir:

Based on the new arguments and comments made of record by the Examiner for the first time during prosecution, Appellant respectfully submits the following reply to the Examiner's Answer mailed on September 30, 2009.

I. The rejection of record fails to establish a *prima facie* obviousness rejection by failing to demonstrate all elements of the claimed invention, based on primary reference Fujimoto

The claimed invention describes <u>both</u> structure and function in all of the independent claims. Therefore, the prior art evaluation must <u>start out</u> by assuming both the structure and function of the cited primary reference.

Appellant has repeatedly requested during prosecution that the Examiner take into account the structure of primary reference Fujimoto and then identify the

Appellant's Reply Brief on Appeal

S/N: 11/372,198

differences and provide a reasonable rationale to modify the structure that is demonstrated in Fujimoto to arrive at the structure of the claimed invention.

The evaluation of record does not follow this fundamental obviousness evaluation and, therefore, fails to provide a *prima facie* obviousness rejection.

Instead, the evaluation of record accounts only for <u>functional</u> similarities but ignores the structure of primary reference Fujimoto.

II. The following technical analysis based on primary reference Fujimoto clearly demonstrates that the Examiner has erred in the prior art evaluation

II(a). The structure clearly described by independent claim 1 requires a director device that manages the I/O of data from an external device and the disk drive device, where the director device has a command control unit that transmits the command for controlling of a cache memory and that receives a processing result.

The <u>only</u> structure in primary reference Fujimoto that would seem to reasonably satisfy this structural/functional description is shown in Figure 7 and would have to be the "Host IF" 102 that corresponds to the "director device" of the claim, and that includes microprocessor 101 that would have to correspond to the "command control unit" of the claim (e.g., see lines 6-9 of column 7).

II(b). Claim 1 also clearly describes a "shared memory device having a cache memory" and having a "processing unit" that executes control of the cache memory and that has a "command control unit" that receives commands from the director device's command control unit, and that transmits the processing result back to the command control unit.

The <u>only</u> structure in primary reference Fujimoto that would seem to reasonably satisfy this structural/functional description is shown in Figure 7 and would have to be the "Cache Memory Unit" 14 described as having a cache memory 109 and controller 108 (e.g., see lines 43-45 of column 7).

II(c). The final claim limitation of claim 1 also clearly describes that a serial bus interconnects the command control unit of the director device with the command control unit of the shared memory device.

There clearly is no serial bus interconnecting microprocessor 101 with CM controller 108 in Figure 7 of Fujimoto. Therefore, the Examiner has the initial burden of providing a reasonable rationale (e.g., one of the seven rationales set out in KSR) to modify the structure shown in Figure 7 of Fujimoto to incorporate a serial data bus between microprocessor 101 and CM controller 108.

The closest attempt in the rejection of record that attempts to address this aspect of the claimed invention the Examiner's new argument, presented for the first time in the Examiner's Answer in paragraph (10) on page 17:

"The specific type of bus is not disclosed by Fujimoto, however, there are two types of busses that [exist] for this purpose, parallel or serial. Each bus has its own advantages, and it would have been obvious to try each of these busses, since there are a limited number of choices, in an attempt to solve the problem of connecting these devices together. Furthermore, when the combination of Fujimoto and Millard is made there would be additional processors for the shared memory devices. This would result in an interconnection of multiple processors, which Millard disclosed can be done with a serial bus (see column 2, line 60)."

Appellant submits that there are at least three problems with the Examiner's new argument recited above and that this rationale is insufficient to demonstrate obviousness.

First, as explained in paragraph [0009] of the disclosure of the present application, the conventional wisdom for interconnecting two processors used for disk array devices is by way of using a <u>shared bus</u>. In contrast, the final limitation of the claimed invention explicitly requires that a serial communication bus be used for transmission of commands and processing results. All of the references of record, including primary reference Fujimoto, appear to follow this conventional architecture of using a shared bus.

Thus, contrary to the conventional wisdom in the art at the time of the invention, the claimed invention modifies the conventional architecture by separating

the bus functions between processors by <u>providing a high speed serial bus dedicated to commands/processing results.</u>

Neither Fujimoto nor Millard suggests separating bus functions in the manner described by the claimed invention. That is, neither reference suggests using a serial command bus in combination with the conventional shared bus that would remain to provide parallel data transmission between processors in a disk array device.

Therefore, even if Millard were considered to be properly combinable with Fujimoto, there would still be no suggestion of providing a dedicated a high speed serial bus specifically for purpose of transmitting commands and returned processing results. The claimed invention separates the transmission paths of data and commands, and uses a high speed serial bus specifically for the command bus, which is not taught or suggested in either cited reference.

Thus, the combination of the claimed invention is <u>more than merely trying</u> a <u>serial bus</u> as a shared bus <u>versus using a parallel bus</u> as the shared bus, as the Examiner alleges in his new argument. Indeed, using a serial bus to replace a parallel bus that is a shared bus would only slow down the overall shared bus transmission, absent some type of objective evidence by the Examiner, which evidence is not currently of record.

Second, as Appellant has repeatedly pointed out during prosecution, the details of the architecture of secondary reference demonstrate a completely different principle of operation from that of primary reference Fujimoto. It is, therefore, not properly combinable under the holding of *In re Ratti*, 270 F.2d 810, 123 USPQ 349 (CCPA 1959), as described in MPEP 2143.01: "If the proposed modification or combination would change the principle of operation of the prior art invention being modified, then the teachings of the references are not sufficient to render the claims prima facie obvious."

That is, the extraction of specific design features from two circuits operating under two fundamentally different principles of operation is clear indication of impermissible hindsight, unless the Examiner demonstrates that the extracted feature is reasonably either a direct substitution performing the identical function in both circuits or provides an improvement in the context of the circuit of the primary reference. In the final sentence on page 4 of the Examiner's Answer, the Examiner himself

characterizes secondary reference Millard as demonstrating a fundamentally different approach (e.g., different principle of operation) from that of primary reference Fujimoto.

Stated slightly differently in the concepts of KSR, since circuits do not function as abstract ideas that can be freely rearranged based upon a roadmap of a claimed invention, extracting a design detail from two references having drastically different architectural details, even if both circuits arguably perform similar functions, would clearly violate the requirement of KSR that the Examiner demonstrate an expectation of success, since the primary reference already performs the similar function without any improvement or substitution of an element of a system having a drastically different configuration. Therefore, the modification of primary reference Fujimoto by Millard is improper in the rejection of record, since there is no reasonable motivation to modify the primary reference and no expectation of success absent impermissible hindsight.

Third, the description involving line 60 of column 2 of Millard, upon which the Examiner relies in the rejection of record, actually recites:

"The communications level processor is configured to communicate with a host computer, an intelligent terminal or other processor devices on either a serial, parallel or DMA basis and performs all communications functions with such external devices, such as handshake, protocol and the like."

Appellant submits that the above-recited description makes no suggestion to incorporate a serial communication bus <u>explicitly for purpose of transmitting</u> <u>commands and receiving processing results</u>, and the most that can reasonably be concluded from the Examiner's new argument is that the Examiner concludes that the claimed invention <u>would have been possible</u> at the time of the invention.

The Examiner's allegation that "... it would have obvious to try each of these busses, since there are a limited number of choices, in an attempt to solve the problem of connecting these devices together" is not supported by objective evidence and does not arrive at the claimed invention, since it is specifically the command bus between two specific processors that is described as using the serial communication bus.

That is, the claimed invention involves <u>more than "merely trying different</u> buses", since it also includes separating the commands/responses from a shared bus

between two specific processors in a disk array device, and incorporating, instead, a serial bus dedicated to commands/responses, as well as using the conventional parallel data bus for the data between these two processors.

Stated slightly differently, if the Examiner's allegation were correct that it would be "obvious to try each of different busses", then there would clearly be no burden on the Examiner to demonstrate, by objective evidence, at least one example of such configuration described in the independent claims. The failure to provide any objective evidence is clear indication of improper hindsight.

Thus, the Examiner's newly-articulated reliance on "obvious to try" is clearly misplaced, since the Appellant's own evaluation above demonstrates that the element missing from primary reference Fujimoto is more than a mere substitution of allegedly "obvious to try" alternatives.

That is, rather than merely "trying" a serial bus rather than a parallel bus, a key difference between the claimed invention and primary reference Fujimoto is that the shared bus of the conventional architectural wisdom is modified to provide a high speed serial bus dedicated to transporting command/process reports between two of the processors in a disk array device. None of the references of record demonstrate this claim element, and the rejection of record fails to properly identify this difference.

III. The evaluation of record fails to comply with the requirements set forth in KSR describing that the Examiner has the initial burden to identify the differences from the primary reference (i.e., Fujimoto) and then provide an articulation of a reasonable rationale to modify that primary reference to arrive at the claimed invention

That is, in ignoring the structure described in the claimed invention, the rejection of record has also failed to properly recognize the differences between primary reference Fujimoto and the claimed invention, since the claimed invention involves more than the mere replacement of the shared bus demonstrated in the prior art references. Rather, the claimed invention actually describes two processors in a disk array device having a bus dedicated to commands and process reports.

The Examiner's new argument based on "obvious to try" is misplaced, since the difference between Fujimoto and the independent claims is not a simple substitution of

Appellant's Reply Brief on Appeal

S/N: 11/372,198

a limited number of known alternatives. Rather, the claimed invention involves a

modification to the shared bus conventionally used in disk array devices.

#### **CONCLUSION**

In view of the foregoing, Appellant submits that the Examiner has clearly erred in the rejections currently of record and that claims 1, 3-17, and 19-31, all the claims presently pending in the application, are patentably distinct over the prior art of record and are in condition for allowance. Thus, the Board is respectfully requested to reverse all rejections of claims 1, 3-17, and 19-31.

Please charge any deficiencies and/or credit any overpayments necessary to enter this paper to Attorney's Deposit Account number 50-0481.

Respectfully submitted,

Dated: 11/30/09

Frederick E. Cooperrider Reg. No. 36,769

McGinn Property Law Group, PLLC 8231 Old Courthouse Road, Suite 200 Vienna, VA 22182-3817

(703) 761-4100

Customer Number: 21254

Doc Code: TRAN.LET Recument Description: Transmittal Letter PTO/SB/21 (07-09) Approved for use through 07/31/2012. OMB 0651-0031 Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number. U.S. Patent and Trademark Office: U.S. DEPARTMENT OF COMMERCE Application Number 11/372,198 TRANSMITTAL Filing Date March 10, 2006 **FORM** First Named Inventor Atsushi KUWATA Art Unit 2186 (to be used for all correspondence after initial filing) **Examiner Name** Edward J. Dudek, Jr. Total Number of Pages in This Submission Attorney Docket Number MA-674-US **ENCLOSURES** (Check all that apply) After Allowance Communication Fee Transmittal Form Drawing(s) Appeal Communication to Board Fee Attached Licensing-related Papers of Appeals and Interferences Appeal Communication to TO Amendment / Reply Petition (Appeal Notice, Brief, Reply Brief) Petition to Convert to a After Final Proprietary Information Provisional Application Power of Attorney, Revocation Affidavits/declaration(s) Status Letter Change of Correspondence Address Other Enclosure(s) (please Extension of Time Request Terminal Disclaimer identify below): Express Abandonment Request Request for Refund CD, Number of CD(s) Information Disclosure Statement Landscape Table on CD Certified Copy of Priority Document(s) Remarks Reply to Missing Parts/ Incomplete Application Reply to Missing Parts under 37 CFR 1.52 or 1.53 SIGNATURE OF APPLICANT, ATTORNEY, OR AGENT Firm Name McGinn Intellectual Property Law Group, PLLC 8321 Old Courthouse Road, Suite 200, Vienna, Virginia 22182 Signature

CERTIFICATE OF TRANSMISSION/MAILING

I hereby certify that this correspondence is being facsimile transmitted to the USPTO or deposited with the United States Postal Service with sufficient postage as first class mail in an envelope addressed to: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450 on the date shown below:

Signature

Typed or printed name

Date HAND DELIVERED

Reg. No.

36,769

Frederick E. Cooperrider, Esq.

November 30, 2009

Printed name

Date

This collection of information is required by 37 CFR 1.5. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to 2 hours to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

new

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| APPLICATION NO.           | FILING DATE                        | FIRST NAMED INVENTOR     | ATTORNEY DOCKET NO. | CONFIRMATION NO. |

|---------------------------|------------------------------------|--------------------------|---------------------|------------------|

| 11/372,198                | 03/10/2006                         | Atsushi Kuwata           | MA-674-US           | 4344             |

|                           | 7590 10/20/200<br>ELLECTUAL PROPEI | 9<br>RTY LAW GROUP, PLLC | EXAM                | INER             |

| 8321 OLD COU              | JRTHOUSE ROAD                      | DUDEK JR, EDWARD J       |                     |                  |

| SUITE 200<br>VIENNA, VA 2 | 22182-3817                         |                          | ART UNIT            | PAPER NUMBER     |

|                           |                                    |                          | 2186                |                  |

|                           |                                    |                          |                     |                  |

|                           |                                    |                          | MAIL DATE           | DELIVERY MODE    |

|                           |                                    |                          | 10/20/2009          | PAPER            |

Please find below and/or attached an Office communication concerning this application or proceeding.

The time period for reply, if any, is set in the attached communication.

## **UNITED STATES DEPARTMENT OF COMMERCE U.S. Patent and Trademark Office**

Address: COMMISSIONER FOR PATENTS

P.O. Box 1450

Alexandria, Virginia 22313-1450

| APPLICATION NO./<br>CONTROL NO. | FILING DATE                  | FIRST NAMED INVENTOR / PATENT IN REEXAMINATION |               | ATTORNEY DOCKET NO. |

|---------------------------------|------------------------------|------------------------------------------------|---------------|---------------------|

| 11372198                        | 3/10/2006                    | KUWATA, ATSUSHI                                | MA-674-US     |                     |

|                                 |                              |                                                | EXAMINER      |                     |

| 8321 OLD COURTHO                | UAL PROPERTY LAW<br>JSE ROAD | Ed                                             | ward J. Dudek |                     |

| SUITE 200<br>VIENNA, VA 22182-3 | 817                          | ART UNIT                                       | PAPER         |                     |

|                                 |                              |                                                | 2186          | 20091019            |

DATE MAILED:

Please find below and/or attached an Office communication concerning this application or proceeding.

#### **Commissioner for Patents**

The information disclosure statement (IDS) submitted on 20 April 2009 and 16 September 2009 were filed after the mailing date of the advisory action on 05 March 2009. The submission is in compliance with the provisions of 37 CFR 1.97. Accordingly, the information disclosure statement is being considered by the examiner.

/Edward J Dudek/ Examiner, Art Unit 2186 /Pierre-Michel Bataille/ Primary Examiner, Art Unit 2186

| Receip               | ot da | te: 04/20/2009  RMATION DISCLOSURE  (Use several sheets if necessal  | APR 2            | 0 2009                                | Pocket Number (Optional)  MA-674-US | s 1 1              | polication Number     | GAU: 2             | 2186         |

|----------------------|-------|----------------------------------------------------------------------|------------------|---------------------------------------|-------------------------------------|--------------------|-----------------------|--------------------|--------------|

|                      | INFO  | (Use several sheets if necessar                                      | CITATION         | , <b>4</b>                            | Applicant(s)<br>Atsushi KUWATA      |                    |                       |                    |              |

|                      |       | ( 000 000 000 000 000 000 000 000 000 0                              | To Day           | 3                                     | Filing Date                         |                    | roup Art Unit         |                    |              |

|                      |       |                                                                      | ્યા <u>.</u>     | <b>3</b> /A**                         | March 10, 20                        | 06                 |                       | 186                |              |

|                      |       |                                                                      | U.S              | . PATENT                              | DOCUMENTS                           |                    | -                     |                    |              |

| *EXAMINER<br>INITIAL | REF   | DOCUMENT NUMBER                                                      | DATE             |                                       | NAME                                | CLASS              | SUBCLASS              | FILING<br>IF APPRO |              |

|                      | al    | 6,477,619 B1                                                         | 11/05/2002       | Fujimot                               | o et al.                            |                    | <del> </del>          |                    |              |

|                      |       | 6,915, <b>3</b> 89 B2                                                | 07/05/2005       | Fujimot                               | 0                                   |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       | ł.,                |              |

|                      |       |                                                                      | U.S. PATENT      | Γ APPLICA                             | TION PUBLICATIONS                   |                    |                       |                    |              |

| *EXAMINER<br>INITIAL | REF   | DOCUMENT NUMBER                                                      | DATE             |                                       | NAME                                | CLASS              | SUBCLASS              | FILING<br>IF APPRO |              |

|                      | == -  |                                                                      |                  | · · · · · · · · · · · · · · · · · · · |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      | FORE             | IGN PATE                              | NT DOCUMENTS                        |                    |                       |                    |              |

|                      | REF   | DOCUMENT NUMBER                                                      | DATE             |                                       | COUNTRY                             | CLASS              | SUBCLASS              | Trans<br>YES       | lation<br>NO |

|                      |       | 2000-10900 A                                                         | 01/14/2000       | Japan                                 |                                     |                    |                       | ABS                |              |

|                      |       | 2001-256003 A                                                        | 09/21/2001       | Japan                                 |                                     |                    |                       | ATS                |              |

| 9                    |       | 2003-280824 A                                                        | 10/02/2003       | Japan                                 |                                     |                    |                       | AB                 |              |

| è                    |       |                                                                      |                  |                                       |                                     |                    |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    | <u> </u>              |                    |              |

|                      |       |                                                                      |                  | OCUMEN                                |                                     |                    | ertinent Pages, E     | tc.)               |              |

|                      |       | Japanese Office Action                                               | February 2, 2009 | with Part                             | ial English-Language Tra            | anslation          |                       |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    | -                     |                    |              |

|                      |       |                                                                      |                  |                                       |                                     |                    | _                     |                    |              |

| EXAMINE              | R     | /Edward Dudek Jr/                                                    |                  |                                       | DATE CONSIDERED                     | 09/28/20           | )09                   |                    |              |

|                      |       | al if citation considered, whether clude copy of this form with next |                  |                                       | ce with MPEP Section 609;           | Draw line throu    | igh citation if no    | t in conform       | ance and     |

| Form PTO             |       |                                                                      |                  |                                       | VREV05                              | Patent and Tradema | ark Office * U.S. DEI | PARTMENT OF        | COMMERCE     |

OHE

(also form PTO-1449)

SHEET 1 OF 1

| Recei                 | nt d         | ate.                                             | Ŏ9/16/2009                                                 | <del></del>          |                                                  | ATTY DOCKET NO.                            |               | APPLICATION N          |            | 7            |

|-----------------------|--------------|--------------------------------------------------|------------------------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------|---------------|------------------------|------------|--------------|

|                       |              |                                                  | TION DISCLOSURE                                            | CITATRANIA           |                                                  | MA-674-US<br>APPLICANT(S)                  |               |                        | 372.198    |              |

|                       | INFC         | r IVIA<br>- 1.1/                                 | e several sheets if necess                                 |                      | ጭ /                                              | Atsushi KUWATA                             | 1             | 1372198 -              | GAU:       | 2186         |

|                       |              | (US                                              | e several sneets if necess                                 | 40 no                |                                                  | FILING DATE                                |               | GROUP ART UN           |            |              |

|                       |              |                                                  |                                                            | 018 20               | E)                                               |                                            | _             |                        |            |              |

|                       |              |                                                  |                                                            | SEP 1 6 20           | 5                                                | March 10, 2006                             | <u> </u>      | 2                      | 2186       |              |

| U.S. PATÉNT DOCUMENTS |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

| *EXAMINER             | -            |                                                  | DOCUMENT NUMBER                                            | DATE DATE            |                                                  | NAME                                       | CLASS         | SUBCLASS               | FILING DAT |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            | -             |                        |            |              |

| İ                     |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

| i                     |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              | i                                                |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            | <del></del>          |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      | ĺ                                                |                                            |               |                        |            |              |

|                       |              | <del>                                     </del> |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      | ]                                                |                                            |               | İ                      |            |              |

| ·                     |              |                                                  |                                                            | U.C. DATEN           | T ADDI IC                                        | ATION BURBLICATIONS                        |               |                        | <u> </u>   |              |

|                       |              |                                                  |                                                            | U.S. PATEN           | II APPLIC                                        | ATION PUBLICATIONS                         |               |                        |            |              |

| EXAMINER              |              |                                                  | DOCUMENT NUMBER                                            | DATE                 |                                                  | NAME                                       | CLASS         | SUBCLASS               | FILING DAT | E            |

| INITIAL               |              |                                                  | DOCUMENT NUMBER                                            | DATE                 |                                                  | NAME                                       | CLASS         | SUBCLASS               | IF APPROF  | PRIATE       |

|                       |              |                                                  | and Mal                                                    |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        | l          |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              | -                                                |                                                            |                      | ļ                                                |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            | _            |

|                       |              |                                                  |                                                            | į                    |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  | ·                                                          |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        | <u> </u>   |              |

|                       |              |                                                  |                                                            | FORE                 | IGN PATE                                         | ENT DOCUMENTS                              |               |                        |            |              |

|                       |              |                                                  | DOCUMENT NUMBER                                            | DATE                 |                                                  | COUNTRY                                    | CLASS         | SUBCLASS               | TRANS      | LATION<br>NO |

|                       |              | 2003                                             | 2-328850                                                   | 11/15/2002           | Japan                                            |                                            |               |                        | 1          |              |

| •                     |              | -                                                |                                                            |                      | ļ                                                | <del></del>                                |               |                        | AMS        |              |

|                       |              | 2002                                             | 2-351622<br>                                               | 12/06/2002           | Japan                                            |                                            |               |                        | Abg        |              |

|                       | <u> </u>     | 2004                                             | 4-171177                                                   | 06/17/2004           | Japan                                            |                                            |               |                        | Alos       | 1            |

|                       |              | 200                                              | 4-213125                                                   | 07/29/2004           | Japan                                            | -                                          |               |                        | Abs        |              |

|                       | <del> </del> | <del>  </del>                                    |                                                            | 00/06/2004           | <del>                                     </del> |                                            | <u> </u>      |                        | 1 .        |              |

|                       |              | 200                                              | 4-240949                                                   | 08/26/2004           | Japan                                            |                                            | <u> </u>      |                        | Alos       |              |

|                       |              |                                                  | OTHER DOCUME                                               | NTS (Includia        | ng Autho                                         | r, Title, Date, Pe <mark>rti</mark> nent l | Pages, Et     | c.)                    |            |              |

|                       |              |                                                  | Jananese Office Actic                                      | •                    | -                                                | with partial English tran                  |               |                        |            |              |

|                       | [            |                                                  | Japanese Office Activ                                      | m dated bune s       | .0, 2005 (                                       | with put that English than                 | .0141.011)1   |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       | 1            |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

| EXAMINE               | R            |                                                  |                                                            |                      |                                                  | DATE CONSIDERED                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      |                                                  |                                            |               |                        |            |              |

|                       |              |                                                  |                                                            |                      | - i=f-                                           | manae with MDED 000: D                     | line through  | h citation if not in   | conforman  | e and not    |

| *EXAMINE              | ER: Ini      | tial if re                                       | eference considered, wheth<br>py of this form with next co | er or not citation i | s in contor<br>policant                          | mance with MPEP 609; Draw                  | iine inroug   | n diadon ii notin      | comornanc  | e and not    |

| considered            | u. Incl      | uue co                                           | py or una form with next co                                | annumoation to a     | ppiloditi.                                       |                                            |               |                        |            |              |

| Form PTO              | -A820        |                                                  |                                                            |                      | P09                                              | PaC/REV04 Pa                               | tent and Trad | emark Office * U.S. DE | PARTMENT O | FCOMMERCE    |

(also form PTO-1449)

PAGE ( OF 2

| Receipt       | date:        | 09/16/2009                                                    | CEP I         | 8 2009 A   | MA-674-US                     |                    | 11/:                 | 372,198                                          |           |

|---------------|--------------|---------------------------------------------------------------|---------------|------------|-------------------------------|--------------------|----------------------|--------------------------------------------------|-----------|

| INF           | ORMA<br>U:   | 09/16/2009<br>ATION DISCLOSURE<br>se several sheets if necess | CITATION (    | de la      | Atsushi KUWATA                |                    | 1372198              | - GAU:                                           | 2186      |

|               |              |                                                               | TIENTS        | TRADEMA    | FILING March 10, 20           |                    | ROUP ART             | 2186                                             |           |

|               | -            |                                                               | U.S           | S. PATENT  | DOCUMENTS                     |                    |                      |                                                  |           |

| *EXAMINER   * |              | DOCUMENT NUMBER                                               | DATE          |            | NAME                          | CLASS              | SUBCLASS             | FILING DATE                                      |           |

| MITTAL        |              |                                                               |               |            |                               |                    |                      | II ALTROIT                                       | VATE.     |

|               |              |                                                               |               |            |                               |                    |                      |                                                  |           |

|               |              |                                                               |               |            |                               |                    |                      | <del>                                     </del> |           |

|               |              |                                                               |               |            |                               |                    |                      |                                                  |           |

|               |              |                                                               |               |            |                               |                    |                      |                                                  |           |

|               | <u> </u>     |                                                               | II S DATE     | NT APPLIC  | ATION PUBLICATIONS            |                    |                      | <u> </u>                                         |           |

| *EXAMINER     |              | DOCUMENT AND ACCOUNT                                          | Υ             | TI AFFEIG  |                               | 01.422             | eliber too           | FILING DATI                                      |           |

| INITIAL       |              | DOCUMENT NUMBER                                               | DATE          |            | NAME                          | CLASS              | SUBCLASS             | IF APPROPE                                       |           |

|               | _            |                                                               | 1             |            |                               | _                  |                      |                                                  |           |

|               |              |                                                               |               |            |                               |                    |                      |                                                  |           |

|               |              | <u></u>                                                       |               |            |                               |                    |                      |                                                  |           |

|               |              |                                                               |               |            |                               |                    |                      |                                                  |           |